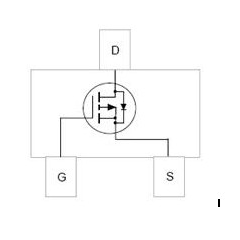

D-FET is yn 'e 0 poarte bias doe't it bestean fan kanaal, kin fiere de FET; E-FET is yn 'e 0 poarte bias as d'r gjin kanaal is, kin de FET net útfiere. dizze twa soarten FET's hawwe har eigen skaaimerken en gebrûk. Yn it algemien, ferbettere FET yn hege-snelheid, low-power circuits is tige weardefol; en dit apparaat wurket, it is de polariteit fan de poarte bias voltage en drain spanning fan itselde, it is handiger yn circuit design.

De saneamde ferbettere middels: doe't VGS = 0 buis is in cut-off steat, plus de krekte VGS, de mearderheid fan dragers wurde oanlutsen ta de poarte, dus "ferbetterje" de dragers yn 'e regio, it foarmjen fan in conductive kanaal. n-kanaal ferbettere MOSFET is yn prinsipe in lofts-rjochts symmetryske topology, dat is de P-type semiconductor op it generearjen fan in laach fan SiO2 film isolaasje. It genereart in isolearjende laach fan SiO2-film op 'e P-type semiconductor, en diffúsearret dan twa tige doped N-type regio's trochfotolitografy, en liedt elektroden út de N-type regio, ien foar de drain D en ien foar de boarne S. In laach fan aluminium metaal wurdt plated op de isolearjende laach tusken de boarne en de drain as de poarte G. As VGS = 0 V , der binne nochal wat diodes mei efterinoar diodes tusken de drain en de boarne en de spanning tusken D en S foarmet gjin stroom tusken D en S. De stroom tusken D en S wurdt net foarme troch de spanning oanbrocht.

As de poartespanning tafoege wurdt, as 0 <VGS <VGS(th), troch it kapasityf elektryske fjild dat wurdt foarme tusken de poarte en it substraat, wurde de polyongatten yn 'e P-type semiconductor tichtby de boaiem fan' e poarte nei ûnderen ôfset, en in tinne útputting laach fan negative ioanen ferskynt; tagelyk, it sil lûke de oligonen dêryn te ferpleatsen nei it oerflak laach, mar it oantal is beheind en net genôch om te foarmjen in conductive kanaal dat kommunisearret de drain en boarne, dus it is noch net genôch te Formaasje fan drain hjoeddeistige ID. fierdere ferheging VGS, doe't VGS > VGS (th) (VGS (th) wurdt neamd de turn-on spanning), omdat op dit stuit de poarte spanning hat west relatyf sterk, yn de P-type semiconductor oerflak laach tichtby de boaiem fan 'e poarte ûnder it sammeljen fan mear elektroanen, kinne jo foarmje in geul, de drain en de boarne fan kommunikaasje. As de drain boarne spanning wurdt tafoege op dit stuit, kin de drain hjoeddeistige wurde foarme ID. elektroanen yn de conductive kanaal foarme ûnder de poarte, fanwege de carrier gat mei de P-type semiconductor polariteit is tsjinoerstelde, dus it hjit anti-type laach. As VGS bliuwt te fergrutsjen, sil ID fierder te fergrutsjen. ID = 0 by VGS = 0V, en de drainstrom komt pas nei VGS> VGS (th), dus, dit type MOSFET hjit ferbettering MOSFET.

De kontrôlerelaasje fan VGS op drainstream kin wurde beskreaun troch de kromme iD = f(VGS(th))|VDS=const, dy't de transferkarakteristike kromme neamd wurdt, en de omfang fan 'e helling fan' e transferkarakteristike kromme, gm, wjerspegelet de kontrôle fan drain hjoeddeistige troch de poarte boarne spanning. de grutte fan gm is mA/V, dus gm wurdt ek wol de transkonduktânsje neamd.